Исследователи безопасности расширили существующие незафиксированные недостатки конструкции процессоров Intel и обнаружили новый способ утечки конфиденциальной информации между ядрами.

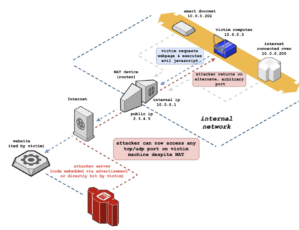

Исследователи из поставщика безопасности VUSec изучили поведение сложных инструкций x86 и обнаружили недокументированный промежуточный буфер или область памяти в процессорах Intel, которая является общей для всех ядер и содержит конфиденциальные данные.

Используя микроархитектурные атаки на выборку данных «Fallout», исследователи смогли собрать данные из приложений, работающих в защищенных анклавах расширения Intel Software Guard, таких как частные ключи цифровой подписи.

Это первый случай, когда межъядерные спекулятивные атаки исполнения стали возможными, и они не полагаются на симметричную многопоточность (SMT), также известную как гиперпоточность.

Помимо высококлассных серверов и самых последних процессоров, большинство других процессоров Intel, вероятно, будут уязвимы для перекрестных помех.

Intel называет эту уязвимость Специальной выборкой данных буфера регистра (SRBDS) и выпустила обновление микрокода для поставщиков программного обеспечения, которое смягчает ее воздействие.

Это делается путем блокировки буфера памяти перед обновлением промежуточного буфера и освобождения только после того, как содержимое памяти было очищено, сказал ВУсек.

Однако такая блокировка шины системной памяти влечет за собой значительные накладные расходы на производительность.

Из-за этого Intel решила применять смягчение только к конкретным, критичным для безопасности инструкциям, оставляя другие, которые выдают запросы вне ядра, уязвимыми для утечки.

VUsec работал на уязвимости на протяжении почти двух лет.

Впервые Intel сообщила об утечке одного и того же ядра в сентябре 2018 года, но по мере того, как VUSec развивал атаку дальше, поставщик безопасности сообщил Intel, что то же самое можно сделать на всех процессорных ядрах в июле 2019 года.

Первопричина этого недостатка заключается в том, что Intel не исправила должным образом существующую уязвимость выборки данных микроархитектуры в своей конструкции процессора и вместо этого играла в «ударь-моль» с ее симптомами, сказал ВУсек.